Table of Contents

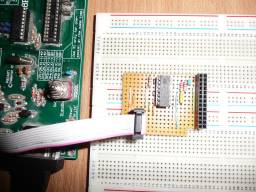

Velleman K8048 interface

We may attach the Velleman K8048 kit to the RPi via a simple interface circuit. This allows us to perform high voltage programming and basic experiments.

GPIO configuration

TX/!MCLR/VPP <- GPIO14 RTS/PGC CLOCK <- GPIO18 DTR/PGD DATA_OUT <- GPIO24 RTS/PGD DATA_IN -> GPIO25

The pins chosen may not be optimal nor your preference. You can change the pins to any you like in your profile.

Circuit schematic

A 74HC(T)03 QUAD TWO INPUT NAND GATE OPEN-DRAIN is used as a voltage level shifter.

Three outputs drive three of four inverting NAND O/D gates and the single input drives the fourth remaining gate.

The 74HC03 device has a typical input high level of 2.6V and works here but is only guaranteed for operation with a 3.5V input level. The 74HCT03 variant of this chip is preferable if available and the HCT has a typical input high level of 1.5V.

+5V------------+----------------------------------------Vcc

|

=== 100n

|

GND------------+------------------------------GND D-SUB-9 5

|--\ +----2K2---Vcc

GPIO14(1)---+--| \ |

| | |O--------+-----------TX/MCLR D-SUB-9 3

+--| /

|--/

|--\ +----2K2---Vcc

GPIO18------+--| \ |

| | |O--------+---------RTS/CLOCK D-SUB-9 7

+--| /

|--/

|--\ +----2K2---Vcc

GPIO24------+--| \ |

| | |O--------+------DTR/DATA_OUT D-SUB-9 4

+--| /

|--/

+----1M(2)----GND

/--| |

/ |--+---+----4K7(3)--CTS/DATA_IN D-SUB-9 8

GPIO25------O| | | _|_

\ |--+ /_\ 5V1 ZENER(3)

\--| |

GND

- When using either GPIO14 or GPIO15 kernel logging and a serial console process must be deactivated on these pins which double up as a UART.

sudo bash cp /etc/inittab /etc/inittab.dist sed -i 's/T0:23:respawn:/#T0:23:respawn:/g' /etc/inittab cp /boot/cmdline.txt /boot/cmdline.txt.dist echo "dwc_otg.lpm_enable=0 console=tty1 root=/dev/mmcblk0p2 \ rootfstype=ext4 elevator=deadline rootwait"> /boot/cmdline.txt sync reboot

- To stop stray noise pickup when the Velleman K8048 is disconnected. This is not required for normal and connected operation.

- Velleman K8076 or compatible serial device only (untested). These are not required for operation with the Velleman K8048.

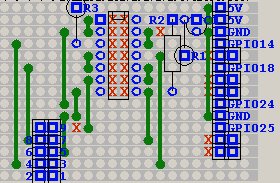

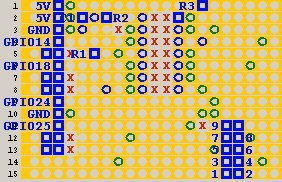

Stripboard layout

On the left we have the component side and to the right the solder (strip) side.

X marks where a track must be cut on the bottom with a stripboard surface cutter.

Components

The serial header above is a standard P.C. motherboard header.

The stripboard is cut with a hacksaw and stanley knife along the centers (lengthwise) of the DIL headers.

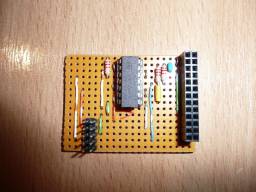

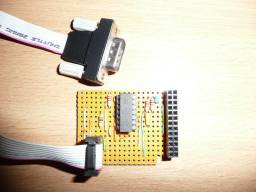

Assembled

Wire links are cut from CW1308 telephone cable.

The finished article has a corner trimmed to fit the R-PI case.

You may wire a pull-down resistor to IC pin 4/5 to GND to stop stray noise pickup when the Velleman K8048 is disconnected. This isn't needed for normal and connected operation.

For the Velleman K8076 (untested) you may replace the second from left link with a resistor then connect a zener diode anode to ground and cathode to IC pin 4/5. There is ample room to accomplish this modification along with the pull-up modification above.

Pickle Microchip PIC ICSP

Configuration

DEVICE=RPI SLEEP=10 BITRULES=0x0010 VPP=14 PGM=-1 PGC=18 PGDO=24 PGDI=25