Table of Contents

STM32F030 DEMO BOARD V1.0

These are cheap development boards with a STM32F030F4P6 Arm Cortex-M0 MCU which contains 16KB flash and 4KB ram.

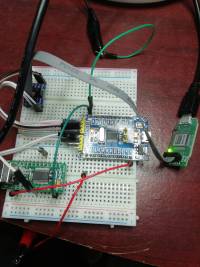

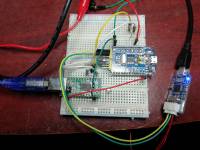

These boards are quite wide and it's wise to attach the headers below only if two breadboards can be utilised side by side (see pictures).

These boards can be programmed using SWD or with the STM serial boot loader in ROM.

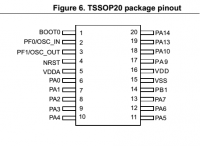

Pinout

USB

RESET POWER

SWITCH LED

BOOT0 5V

PF0 GND BOOT0 3V3 5V

PF1 PA14

NRST PA13

VDDA PA10

PA0 PA9

PA1 PB1

PA2 8MHZ XTAL PA7

PA3 PA6

PA4 LED PA5

GND 3V3

GND 3V3

GND CLK DIO 3V3 RXD TXD GND 3V3

LED PA4

TXD PA9

RXD PA10

DIO PA13

CLK PA14

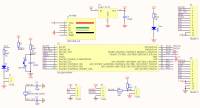

USART1 TX PA2 PA9

USART1 RX PA3 PA10

I2C1 SCL PA9

ICC1 SDA PA10

SPI1 NSS PA4

SPI1 SCK PA5

SPI1 MISO PA6

SPI1 MOSI PA7

Clocks

HSE 8000000 X1 8MHz HSI 8000000 LSE 0 N/A LSI 32768

Power

Power is supplied on the USB socket or the 5V pins. This feeds a 3V3 LDO regulator.

The USB socket does not support I/O, it's only for powering the device.

Test

For testing this board use a UM232R for power, serial comms, reset and a source or external interrupt. Picocom is used to control the reset pin and provide a pulse for testing STM32 EXTI.

Wiring

+--------+ | |TXD-----------RX | FTDI |DTR#----1K----PA0 USB| UM232R |RTS#---390R---NRST | |RXD-----------TX | |GND-----------GND | |USB-----------5V +--------+ +--------+ USB| JLINK/ |DIO-----------DIO | CLONE |CLK-----------CLK +--------+ USB on left is RPi host and USB on right is USB 5V pin on UM232R.

Comms

The lower-rts option to picocom will take the board out of reset and run the program.

picocom --quiet --lower-rts -b 115200 /dev/ttyUSB0

From the RS232 perspective RTS is inverted so when picocom takes the line low, it's actually a high logical output and the board is taken out of reset.

Reset

Picocom CTRL A CTRL G will toggle the RTS line state.

Reboot

If the board is sleeping, picocom can reboot the board to prepare it for new programming.

picocom --quiet --lower-rts --baud 115200 --exit-after 0 /dev/ttyUSB0

Pulse

Picocom CTRL A CTRL P will pulse the DTR pin from low to high for 1 second to test EXTI high or low edge.

Programming

Use SWD with J-Link or OpenOCD.

J-Link

This uses the SEGGER J-Link EDU Mini. A command file is created containing the reset command and is issued to the processor.

Reset

/opt/JLink/JLinkExe -commandfile demov1.reset SEGGER J-Link Commander V7.82a (Compiled Oct 31 2022 11:25:49) DLL version V7.82a, compiled Oct 31 2022 11:25:22 J-Link Command File read successfully. Processing script file... J-Link>USB 801011752 Connecting to J-Link via USB...O.K. Firmware: J-Link EDU Mini V1 compiled Oct 21 2022 11:17:52 Hardware version: V1.00 J-Link uptime (since boot): 0d 00h 53m 10s S/N: 801011752 License(s): FlashBP, GDB USB speed mode: Full speed (12 MBit/s) VTref=3.299V J-Link>Device STM32F030F4 J-Link>SelectInterface SWD Selecting SWD as current target interface. J-Link>Speed 4000 Selecting 4000 kHz as target interface speed J-Link>Reset Target connection not established yet but required for command. Device "STM32F030F4" selected. Connecting to target via SWD InitTarget() start InitTarget() end Found SW-DP with ID 0x0BB11477 DPIDR: 0x0BB11477 CoreSight SoC-400 or earlier Scanning AP map to find all available APs AP[1]: Stopped AP scan as end of AP map has been reached AP[0]: AHB-AP (IDR: 0x04770021) Iterating through AP map to find AHB-AP to use AP[0]: Core found AP[0]: AHB-AP ROM base: 0xE00FF000 CPUID register: 0x410CC200. Implementer code: 0x41 (ARM) Found Cortex-M0 r0p0, Little endian. FPUnit: 4 code (BP) slots and 0 literal slots CoreSight components: ROMTbl[0] @ E00FF000 [0][0]: E000E000 CID B105E00D PID 000BB008 SCS [0][1]: E0001000 CID B105E00D PID 000BB00A DWT [0][2]: E0002000 CID B105E00D PID 000BB00B FPB Cortex-M0 identified. Reset delay: 0 ms Reset type NORMAL: Resets core & peripherals via SYSRESETREQ & VECTRESET bit. Reset: Halt core after reset via DEMCR.VC_CORERESET. Reset: Reset device via AIRCR.SYSRESETREQ. J-Link>Exit Script processing completed. OnDisconnectTarget() start OnDisconnectTarget() end

demov1.reset

USB 801011752 Device STM32F030F4 SelectInterface SWD Speed 4000 Reset Exit

OpenOCD

This uses a J-Link clone from China. This example programs and verifies the device before resetting to start execution.

Program

openocd -f "interface/jlink.cfg" -c "transport select swd" -f "target/stm32f0x.cfg" \

-c "program demov1.bin preverify verify reset exit 0x8000000"

Open On-Chip Debugger 0.12.0-rc2+dev-00012-g4e077fdda (2022-11-12-16:05)

Licensed under GNU GPL v2

For bug reports, read

http://openocd.org/doc/doxygen/bugs.html

swd

Info : J-Link ARM-OB STM32 compiled Aug 22 2012 19:52:04

Info : Hardware version: 7.00

Info : VTarget = 3.300 V

Info : clock speed 1000 kHz

Info : SWD DPIDR 0x0bb11477

Info : [stm32f0x.cpu] Cortex-M0 r0p0 processor detected

Info : [stm32f0x.cpu] target has 4 breakpoints, 2 watchpoints

Info : starting gdb server for stm32f0x.cpu on 3333

Info : Listening on port 3333 for gdb connections

[stm32f0x.cpu] halted due to debug-request, current mode: Thread

xPSR: 0xc1000000 pc: 0x08000664 msp: 0x20001000

**pre-verifying**

**Verified OK - No flashing**

** Resetting Target **

shutdown command invoked